## Crosslight Simulation of Hysteresis Characteristics in Thin Film Transistors

#### **Contents**

- Experiments

- Trap models

- Simulated structure and commands

- Results

- Process simulation

- Summary

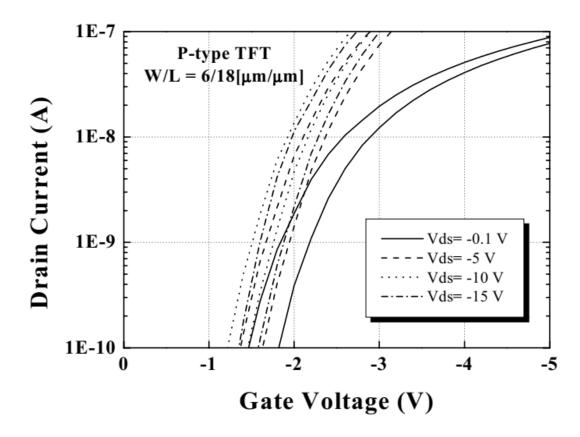

### Hysteresis found in both n-channel and p-channel TFT

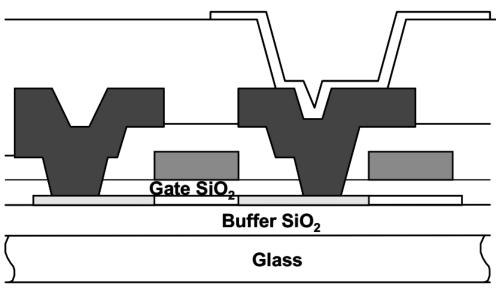

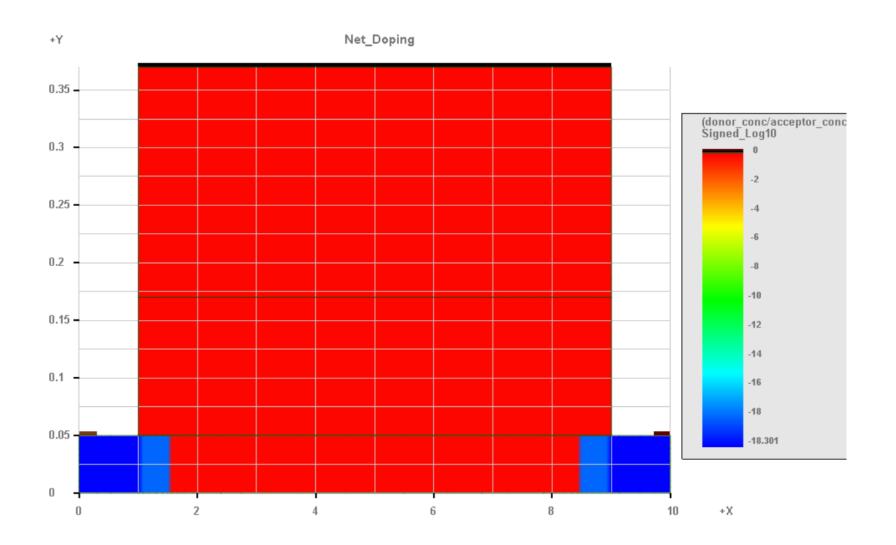

Fig. 1 Cross-sectional view of p-channel TFT

#### Improvement of Hysteresis Characteristics in p-channel Poly-Si TFTs

Byeong-Koo Kim, Ohyun Kim, Hoon-Ju Chung <sup>1</sup>, Sang-Gyu Kim <sup>2</sup>, Chan-Il Park <sup>2</sup>, Hong-Seok Choi <sup>2</sup>, and Yong-Min Ha <sup>1</sup>

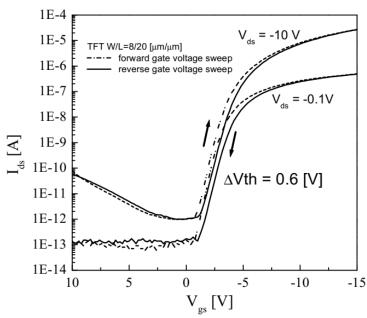

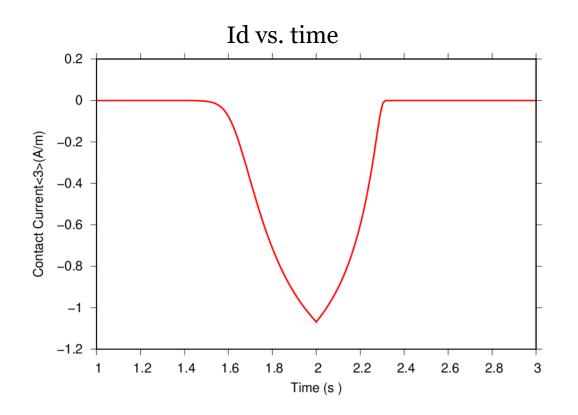

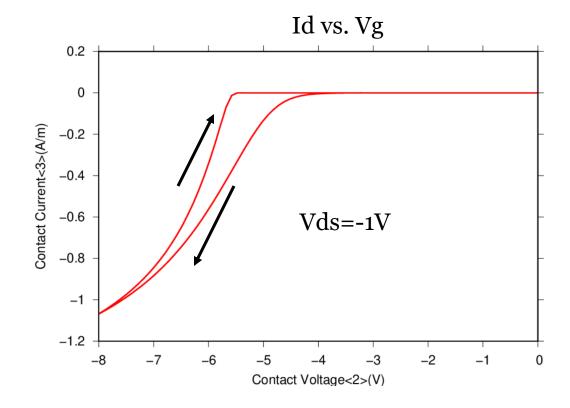

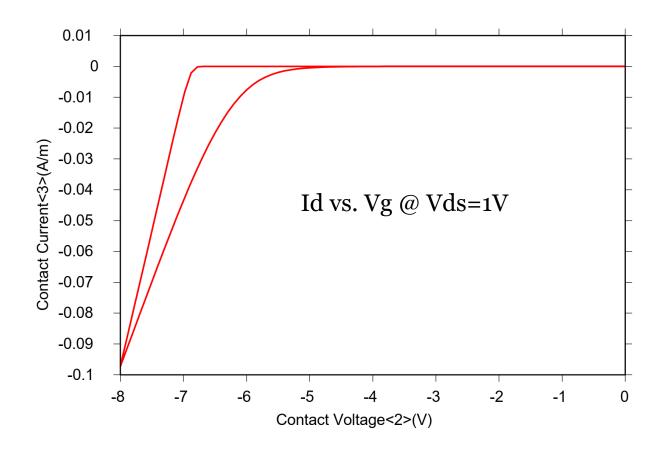

Fig. 2 Ids-Vgs characteristics of p-channel TFT

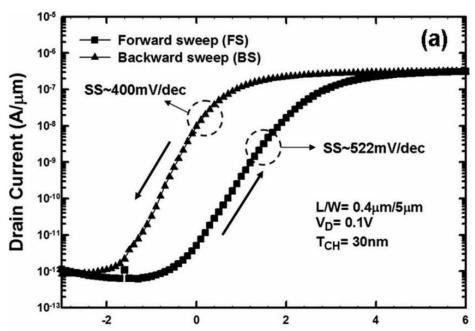

## Hysteresis found in both n-channel and p-channel TFT

#### 1E-7P-type TFT $W/L = 6/18[\mu m/\mu m]$ 1E-8 Drain Current (A) Vds = -0.1 V1E-9 1E-10 $Vgs=10V \sim -5V$ 1E-11 $Vgs=10V \sim -10V$ $Vgs=10V \sim -15V$ $-\cdot -\cdot -\cdot Vgs=10V \sim -20V$ 1E-12 1E-13 -2 -1 -3 -5 Gate Voltage (V)

#### Hysteresis Characteristics in Low Temperature Poly-Si Thin Film Transistors

Hoon-Ju Chung\*a, Dae-Hwan Kimb, and Byeong-Koo Kim\*b

## Hysteresis found in both n-channel and p-channel TFT

Deep level traps were identified as being the cause of hysteresis

JOURNAL OF APPLIED PHYSICS **105**, 054502 (2009)

#### Origin of hysteresis in current-voltage characteristics of polycrystalline silicon thin-film transistors

Horng-Chih Lin, 1,2,a) Cheng-Hsiung Hung, Wei-Chen Chen, Zer-Ming Lin, Hsing-Hui Hsu, and Tiao-Yuang Hunag

#### **Contents**

Experiments

- Trap models

- Simulated structure and commands

- Results

- Summary

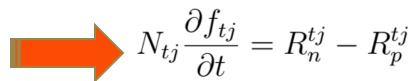

#### **Trap Dynamic Model**

$$-\nabla \cdot \left(\frac{\epsilon_0 \epsilon_{dc}}{q} \nabla V\right) = -n + p + N_D (1 - f_D) - N_A f_A + \sum_j N_{tj} (\delta_j - f_{tj}),$$

$$\nabla \cdot J_n \left(-\sum_j R_n^{tj}\right) - R_{sp} - R_{st} - R_{au} + G_{opt}(t) = \frac{\partial n}{\partial t} + N_D \frac{\partial f_D}{\partial t},$$

$$\nabla \cdot J_p \left(-\sum_j R_p^{tj}\right) + R_{sp} + R_{st} + R_{au} - G_{opt}(t) = -\frac{\partial p}{\partial t} + N_A \frac{\partial f_A}{\partial t}.$$

$$R_n^{tj} = c_{nj} n N_{tj} (1 - f_{tj}) - c_{nj} n_{1j} N_{tj} f_{tj}$$

$$R_p^{tj} = c_{pj} p N_{tj} f_{tj} - c_{pj} p_{1j} N_{tj} (1 - f_{tj})$$

Trapping and detrapping

Traps affect both the space charge and current continuity, and they can be very slow (some deep traps take days to recover since the trapping rates are small)

#### **Contents**

- Experiments

- Trap models

- Simulated structure and commands

- Results

- Process simulation

- Summary

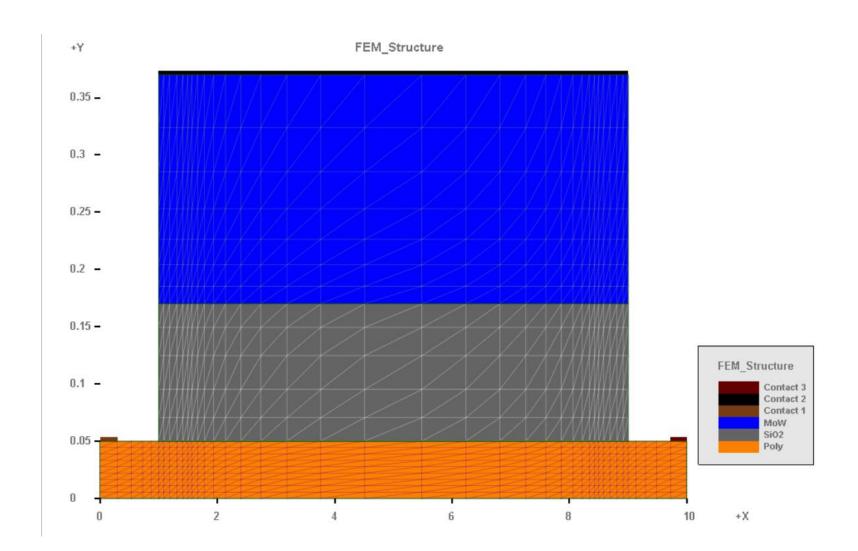

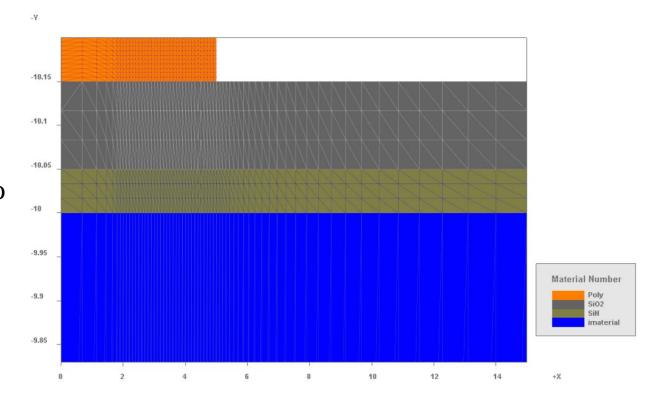

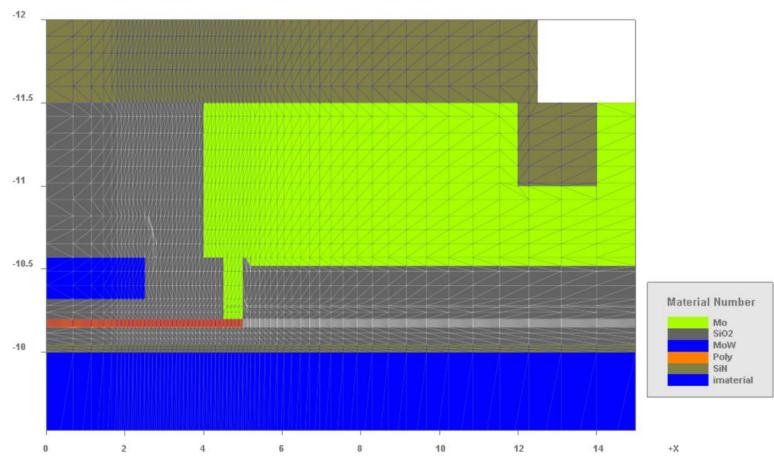

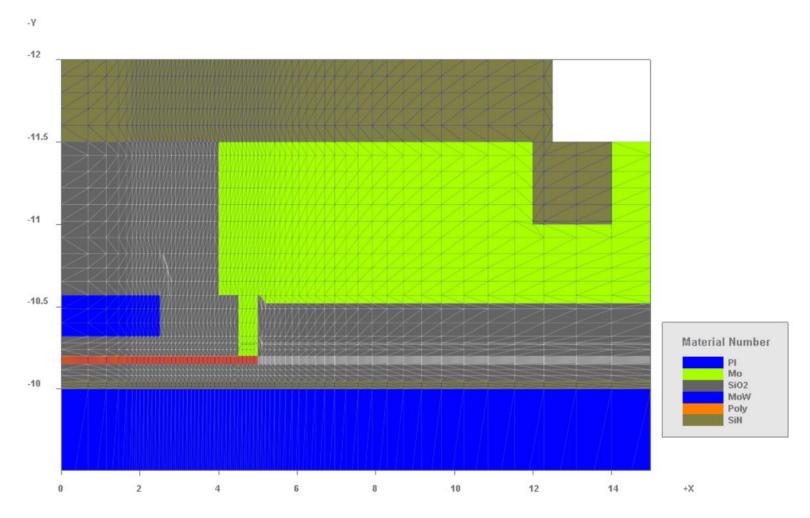

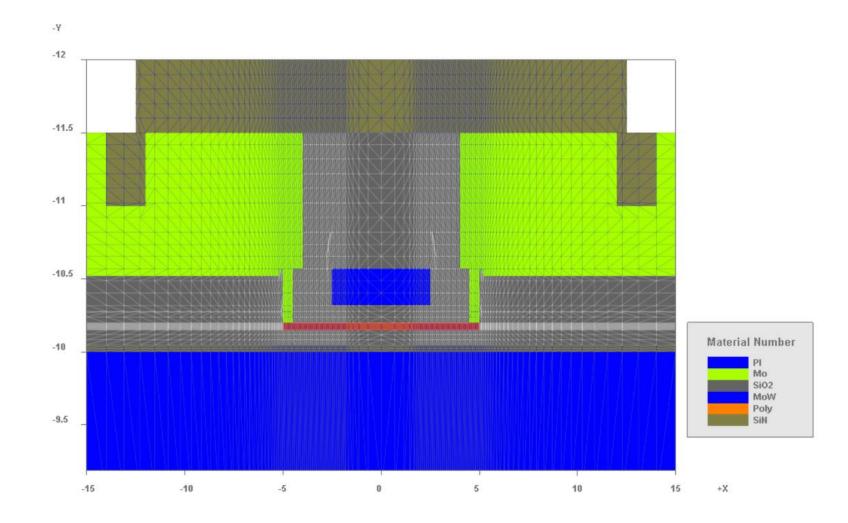

#### Simplified p-channel TFT

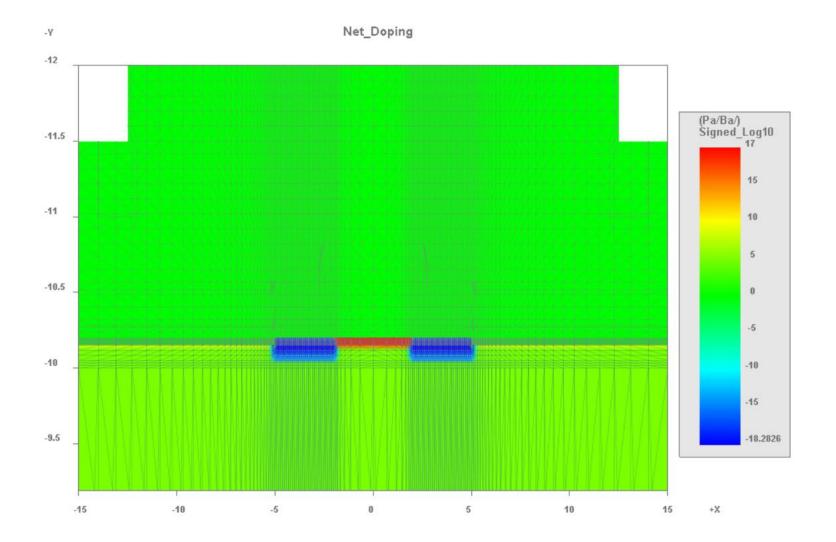

#### Initial net-doping as defined in LayerBuilder

#### **Definition of deep level traps**

```

doping impurity=trap_2 charge_type=donor level=0.65 max_conc=2.e23 && x_prof=(0 20. 0.1 0.1) y_prof=(0 10. 0.1 0.1) trap_ncap_2 value=1.e-23 mater=1 trap_pcap_2 value=1.e-23 mater=1

```

- Trap level calculated from the conduction band edge.

- Use of trap\_2 instead of trap\_1 since trap\_1 is reserved for the usual carrier lifetime setting.

- Ncap or pcap refers to carrier trapping interaction cross section in m<sup>2</sup>. In plain words, carriers interact/scatter with the trap/defect with such this cross section. It should be on the order of or less than the trap/defect area. (nm squared or less).

- Uniform single discrete level trap is the most simple form of carrier trapping while providing well defined space charge. More complicated forms include interface traps and trap with continuous energy level distributions. Crosslight provides a strong and physical TCAD platform for various deep traps.

- Deep level traps originate from crystal defects and are sensitive to growth process conditions

#### **Contents**

- Experiments

- Trap models

- Simulated structure and commands

- Results

- Process simulation

- Summary

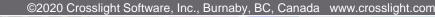

#### Turn on/off characteristics with hysteresis

#### **Contents**

- Experiments

- Trap models

- Simulated structure and commands

- Results

- Process simulation

- Summary

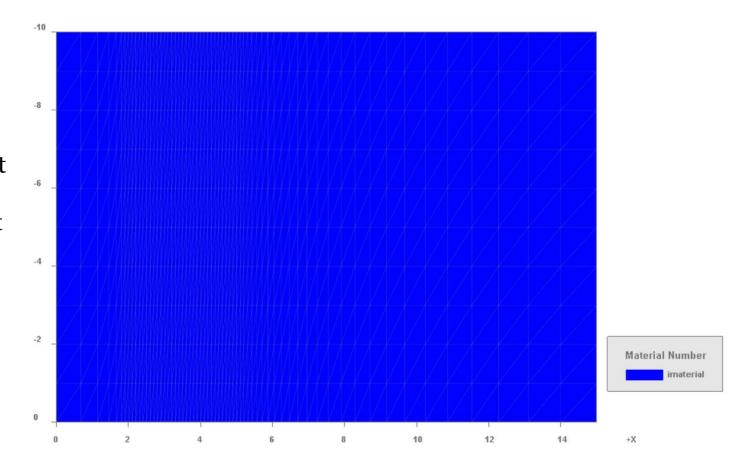

region imaterial xlo=lft xhi=rht ylo=top yhi=bot bound exposed xlo=lft xhi=rht ylo=top yhi=top bound backside xlo=lft xhi=rht ylo=bot yhi=bot

init

struct outf=01\_sub.str

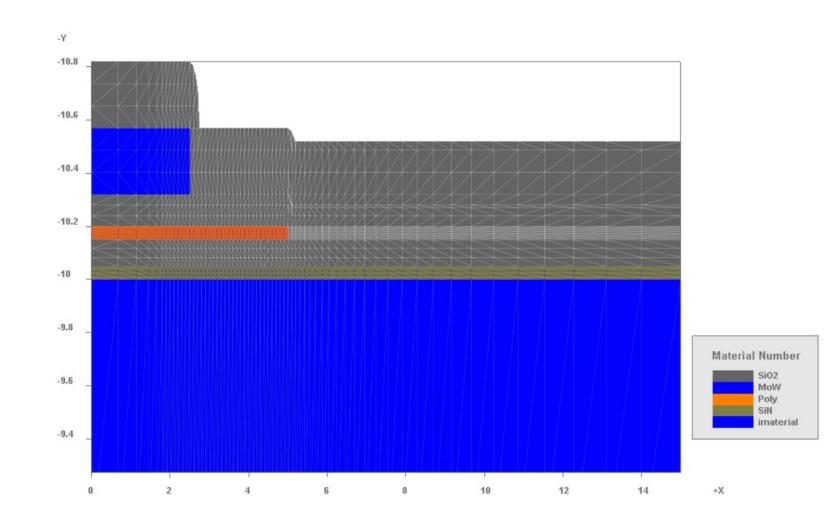

#2\_gate-iso deposit nitride thick=0.05 meshlayer=3 deposit oxide thick=0.1 meshlayer=3

# deposit the gate poly deposit poly phosphorus conc=1.0e17 thick=0.05 meshlayer=10

#4\_source\_drain\_elec mask thick=1. x1.from=0.0 x1.to=2.0 x2.from=5.0 x2.to=15.0 implant boron dose=1e13 energy=15 etch photoresist all

etch poly p1.x=5 right

#anneal diffuse time=5 temp=450

struct outf=02\_ACT.str

#3\_gate\_elec deposit oxide thick=0.12 meshlayer=3 deposit MoW thick=0.25 meshlayer=3 etch MoW p1.x=2.5 right

deposit oxide thick=0.25 meshlayer=3

struct outf=03\_gate\_elec.str

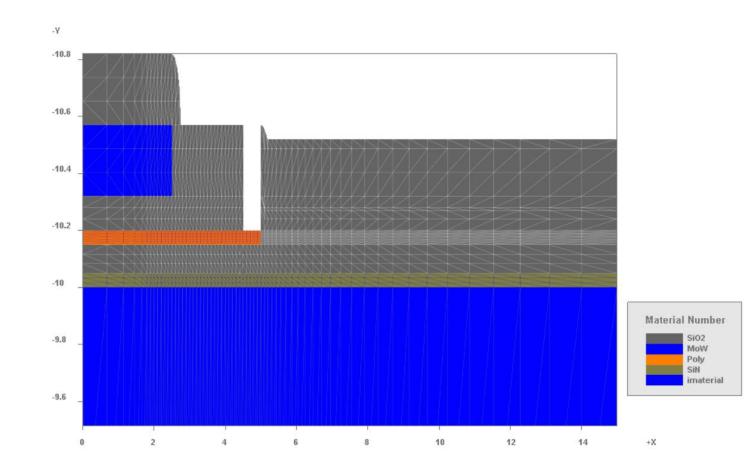

#4\_source\_drain\_elec mask thick=1. x1.from=0.0 x1.to=4.50 x2.from=5.0 x2.to=15.0 etch oxide avoidmask depth=1 etch photoresist all

struct outf=04\_source\_drain\_elec\_1.str

deposit Mo thick=1.0 meshlayer=10 etch Mo p1.x=4.0 left

deposit oxide thick=1.0 meshlayer=10

cmp y=-11.5 above

struct outf=04\_source\_drain\_elec.str

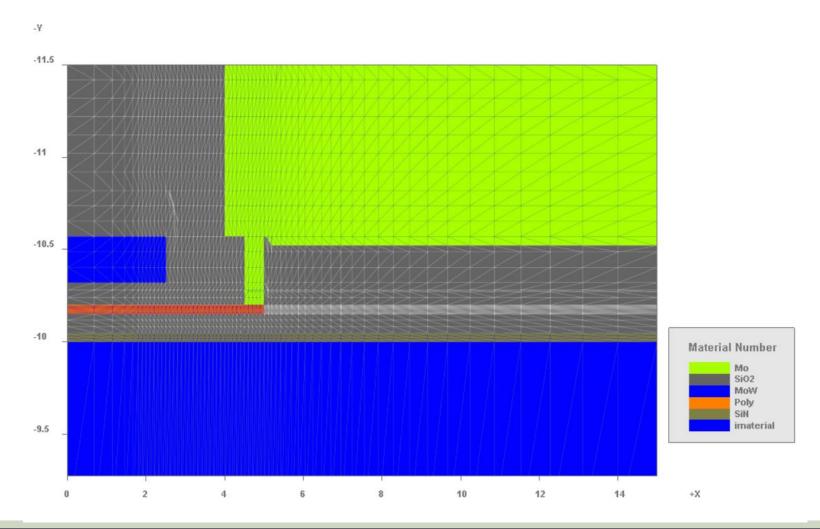

#5-top\_nitride

mask thick=1. x1.from=0.0 x1.to=12.0 x2.from=14.0 x2.to=15.0 etch Mo avoidmask depth=0.5 etch photoresist all

deposit nitride thick=1.0 meshlayer=10 cmp y=-12.0 above

mask thick=1. x1.from=0.0 x1.to=12.5 etch nitride avoidmask depth=0.5 etch photoresist all

struct outf=05\_top\_nitride.str

change\_material imaterial /PI file=PI.txt struct outf=06\_PI.str

# reflect the structure struct mirror left

struct outf=07\_final.str

doping impurity=trap\_2 charge\_type=donor level=0.65 max\_conc=2.e23 && x\_prof=(-15. 15. 0.1 0.1) y\_prof=(0 15. 0.1 0.1) trap\_ncap\_2 value=1.e-23 mater=4 trap\_pcap\_2 value=1.e-23 mater=4

For device simulation, add deep-level traps in its most simple form: single level, uniformly distributed mid-gap donor traps

#### Summary

- ➤ Crosslight provides advanced deep level trap model for TFT (LTPS, IGZO or a-Si)

- > Experimental trends can easily be reproduced

- ➤ Useful for resolving processing/design issues in research or production

# Thanks for your attention!

#### Creators of Award Winning Software